為了優化電路設計以避免EMC(電磁兼容)問題,設計師可以采取一系列措施,這些方法主要集中在信號完整性的保護、合理的PCB布局及使用適當的濾波和屏蔽技術。在深入探討如何通過具體的設計手段來避免EMC問題之前,重要的是先了解導致這些問題的根本原因。

要有效避免EMC問題,需要從源頭減少輻射和傳導干擾的發生。這包括對開關電源的設計優化,如使用軟開關技術減少開關電源產生的高頻諧波;優化數字電路的時鐘信號分布和同步機制,盡可能降低高頻諧波的產生。同時,在電路設計中應避免使用易產生干擾的非線性元件,并確保所有的電路元件都在其線性工作區內運行,以減少互調失真等不良影響。

在信號的考慮方面,高速信號路徑的設計至關重要。必須盡量減少信號路徑中的不連續點,如過孔和直角走線,這些都可能導致信號反射和串擾加劇。此外,對于高速信號,采用差分信號傳輸技術可以顯著提高信號的抗干擾能力,減少信號丟失和錯誤的可能性。

優良的PCB布局是避免EMC問題的關鍵。首先,合理劃分PCB上的區域,將數字電路、模擬電路及電源管理部分相互隔離,可以有效減少它們之間的互相干擾。其次,采用多層PCB設計,并保證電源層與地層之間具有良好電容耦合,利用這種“天然”的電容器效應抑制電源線上的高頻噪聲。同時,對于關鍵信號路徑,應盡量縮短其長度,并使其遠離可能的高干擾源,如大功率驅動器和開關元件。

對于濾波和屏蔽技術的使用,I/O接口處必須采用適當的濾波器設計,以阻止沿信號線傳入或傳出的干擾。例如,可以在接口處設置共模濾波器和差模濾波器,以消除共模和差模噪聲。此外,對于特別敏感的電路部分,采用屏蔽罩可以物理隔離外部的電磁干擾。

除了以上基本策略外,現代電子設計中還常常采用一些技術來進一步優化電路的EMC性能。例如,使用軟件進行前期的EMC風險評估,通過模擬分析發現潛在的EMC問題,在實際生產之前進行調整和優化。這種方法雖然需要較高的技術投入,但能在更早期階段發現問題,從而大幅降低后期修改的成本和時間。

綜上所述,優化電路設計以避免EMC問題是一個涉及多個方面的綜合工程。從理論到實踐,每一步都需要精心設計和嚴格測試。通過實施上述策略,不僅可以有效地預防和解決EMC問題,還可以提高整個系統的穩定性和可靠性,這對于保障產品的質量和市場競爭力具有重要意義。

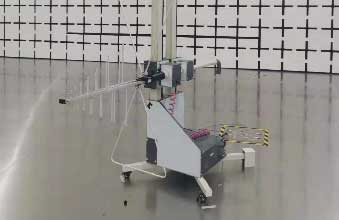

我們華格峰公司是一家專業的EMC產品制造商,我們注重技術創新和服務質量。我們擁有一支專業的研發團隊,不斷推出符合市場需求的新產品和解決方案。同時,我們還提供專業的售前咨詢和售后服務,為客戶提供全方位的支持和保障。如有任何技術和產品問題聯系:13480728051彭經理